이것저것

Design of CMOS PLL ch2(4) 노이즈측면 : Ring Oscillators vs LC Oscillators 본문

Design of CMOS PLL ch2(4) 노이즈측면 : Ring Oscillators vs LC Oscillators

m_jjourney 2025. 7. 18. 21:252.3 Trade-Off Between Phase Noise and Power

2.4 Basic Phase Noise Mechanisms

2.4.1 Phase Noise versus Frequency Noise

2.4.2 Ring Oscillators

2.4.3 LC Oscillators

→ 어떤 oscillator가 noise에 더 강한가 → 구조 선택에 영향을 줌

2.5 Effect of Jitter on Performance

2.6 Effect of Phase Noise on Performance

→ Noise가 실제 회로 성능에 어떻게 영향을 주는지 이해

2.3 Trade-Off Between Phase Noise and Power

' Phase noise 를 줄이려면 더 많은 전력이 필요하다 '

ex) N개의 동일한 오실레이터가 있고 각 오실레이터는 위상노이즈 ϕn1,ϕn2,…,ϕnN 을 가짐

각 오실레이터 출력 : vi(t)=V0cos(ω1t)−V0ϕni(t)sin(ω1t)

이를 모두 더하면 : Vout(t)=NV0cos(ω1t)−V0(ϕn1+⋯+ϕnN)sin(ω1t)

즉, 신호는 N배 커지고, 잡음은 N개가 더해진다.

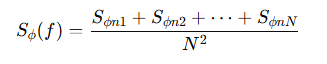

<평균 phase 노이즈 계산>

정규화된 phase 노이즈는 1/ N1(ϕn1+ϕn2+⋯+ϕnN) 와 같다.

이들은 서로 상관없는(uncorrelated) 노이즈이므로, PSD(Power Spectral Density)는

그리고 모든 오실레이터가 동일하다면

즉 총 phase noise는 1/N으로 줄어든다.

<전력과 trade off>

오실레이터 수 N : 위상노이즈 1/N, 전력 N배

oscillator 한개당 소비전력이 P라고 할때, N개면 총 소비전력은

P total = N*P

이때 phase noise는 1/N으로 줄어드므로 phase noise를 N배 줄이려면 전력은 N배 써야한다.

신호는 선형으로 증가하나 노이즈는 제곱근으로 증가하므로

- 이 방법은 이론적으로 가능하지만, 실제로 N개의 발진기 신호를 완벽하게 합산하기는 매우 어려움

- 그래서 실무에서는 다른 방식으로 전력 ↔ 위상 노이즈 Trade-off를 달성하려고 함 (예: bias current, tank Q 등)

- → 이 내용은 3장과 5장에서 더 깊이 다룸

예제 2.16)

앞선 설명에서 N개의 오실레이터 출력을 단순히 더하면 phase noise가 1/N으로 줄어든다고 했는데,

이 실험에서 오실레이터들이 아무리 같은 값으로 시작하더라도

시간이 지나면 각 오실레이터의 위상이 서로 달라지지 않을까?

그러면 출력신호가 서로 파괴적 합성=상쇄(destructive addition) 되어 이론이 깨지는거 아닌가?

답 : 그렇지 않다 이 문제는 걱정할 정도 아님

이유 : phase shift는 아주 천천히 누적되기 때문

오실레이터의 phase noise 즉 jitter는 수백만 주기에 거쳐서야 주기의 일부분만큼 누적됨

짧은시간 scale 안에서는 위상 일치가 유지됨 “coherent”(위상이 같거나 일정한 차이 유지)

2.4 Basic Phase Noise Mechanisms

2.4.1 Phase Noise versus Frequency Noise

Phase noise와 Frequency noise는 어떻게 다를까

먼저 요약하자면 Frequency noise를 적분하면 Phase noise가 된다.

"Frequency noise는 순간 주파수의 흔들림이고, Phase noise는 그 흔들림이 시간에 따라 누적된 결과이다."

제대로 살펴보자

Delay Line 이 있다.

딜레이라인 : 인버터를 여러개 직렬로 연결하여 신호가 인버터의 delay를 거치며 신호가 지연되는 회로이다.

이때 공급전압 VDD가 바뀌면 인버터의 지연시간이 바뀐다. (인버터가 켜지며 올라가는 전압이 커지면 더 오래걸리니까)

지연시간이 바뀌면 결국 입력과 출력 사이의 위상도 바뀐다.

=> 공급 전압 변화 ΔV(노이즈)는 곧 지연 시간 변화(delay) → 위상 변화 Δϕ로 직결됨

노이즈 -> 위상을 바꿈 -> white supply noise -> white phase noise

그래서 다음 parameter의 관계를 세울 수 있다

- : 공급 전압의 작은 변화

- : 그로 인해 생긴 지연 시간의 변화

- KDD: 공급 전압 변화에 따른 supply sensitivity(gain) (delay line의 특성값)

= Δϕ / ΔV - 얼마나 민감하게 위상이 흔들리는지 감도로 표현 - : input output 위상 변화 KDD*Vn

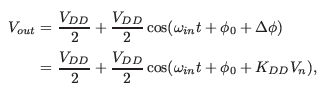

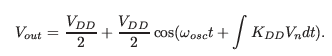

이를 바탕으로 공급 전압에 노이즈 Vn(t) 가 들어갔다고 할때, 출력파형이다

* Delay line 의 출력은 아날로그 신호이고 사인파처럼 진동하나, 완벽한 사인파는 아니지만 주파수와 위상잡음을 분석하려고 최대한 사인파로 근사식을 세운다.

- VDD/2 라는 평균값이 DC offset이고,

- 시간에 따라서 진동하는 성분을 cos으로 표현,

- 출력신호가 본래 형태에서 형태로 바뀐다.

-여기서 ϕ0은 supply voltage에 노이즈가 없을때의 위상이고,

- KDDVn(t)는 공급 노이즈에 의해 추가로 생긴 위상이다.

출력신호는

DC 전압이 VDD/2 이고, DC를 중심으로 움직여서 0-VDD 만큼 움직여야하니까 Amplitude는 VDD/2

이 식은 공급 전압 노이즈 ΔV 가 -> 바로 위상노이즈 Δϕ 로 변환

출력 위상을 직접 진동시키고 있다는 것을 보여줍니다.

만약 가 flicker noise (∝1/f)라면:

- 플리커노이즈 1/f → 위상 잡음스펙트럼은 1/f

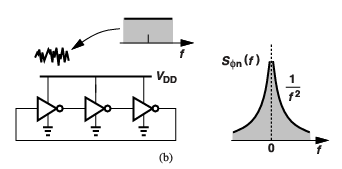

Ring Oscillator가 있다

링오실레이터 동작 : 피드백으로 연결하여 진동주파수를 유지하며 신호가 발진하게 된다.

똑같이 인버터를 사용해 VDD가 노이즈로인해 흔들리면 오실레이터 진동주파수바뀌고 이로인해 위상도 변화한다

(ex : VDD 높아지면 인버터 더 빨리 동작함 -> 오실레이터 주파수 증가)

시간이 지나며 이 변화가 누적된다 -> 주파수 적분은 위상(위상변화 발생)

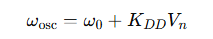

오실레이터의 주파수는 원래 기준 주파수에서 Vn 만큼 K( Δϕ / ΔV ) 의 민감도로 변한다

공급전압이 시간따라 흔들려 오실레이터 주파수 출렁임

공급 전압 VDD가 노이즈 Vn(t)를 가진다면: 진동 주파수가 변화: ωosc(t)=ω0+KDDVn(t)

위상은 주파수의 적분이므로 wosc(노이즈낀 주파수)를 적분하면 다음과 같이 된다.

이런 과정을 통해 주파수변화가 Phase noise까지 만든다.

출력은 DC offset에 위상이 흔들리는것에 노이즈로 인한 것을 포함한 식을 세웠다.

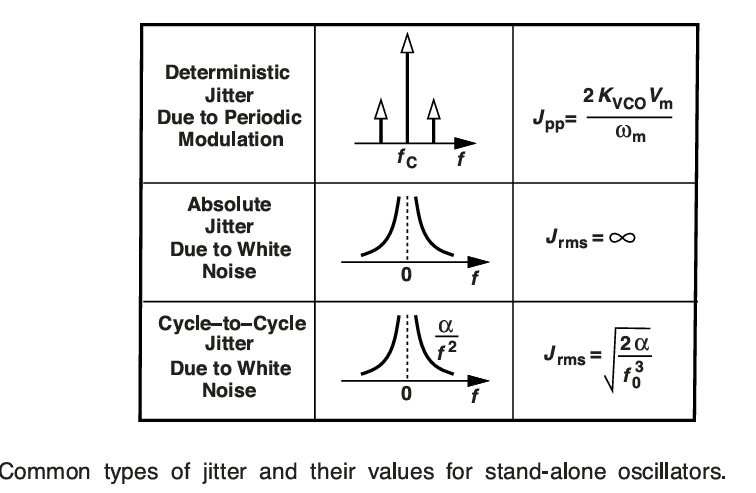

White supply noise → 주파수 노이즈 → 1/f^2 phase noise

가 white noise라면: 주파수 잡음은 white (flat)

→위상 잡음은 주파수 잡음을 적분한 결과

→스펙트럼이 1/f^2 형태가 됨.

만약 가 flicker noise (∝1/f)라면:

- 주파수 잡음이 1/f→ 위상 잡음은 1/f^3

(정리) 스펙트럼 차

Delay line: White phase noise (flat spectrum) 지연 = 위상변화

Ring oscillator: Frequency noise를 적분 → phase noise는 ∝1/{f^2}

링오실레이터의 노이즈 = 주파수 변화 ->

Flicker noise라면:

- Delay line: ∝1/f

- Oscillator: ∝1/f^3

Example 2.17) "무한 길이 delay line은 링 오실레이터랑 같지 않나요?"

sol) No 틀리다.

- Delay line은 노이즈가 위상을 직접 변화시킴 (즉, delay에 의한 위상 shift)

- 반면, Ring Oscillator는 노이즈가 주파수를 바꾸고, 그 주파수를 적분한 결과로 위상이 변함

→ 따라서 noise spectrum의 모양이 완전히 다름!

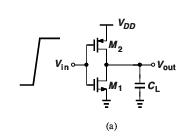

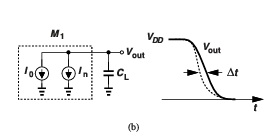

2.4.2 Ring Oscillators

링오실레이터에서 인버터의 노이즈가 phase noise 나 jitter에 어떻게 영향을 주는지 알아보자

이런 cmos inverter 구조에서 입력이 0->VDD 라면 M1이 켜지면서 CL을 VDD 에서 0으로 방전시키게 된다.

M1을 잡음전류 In을 포함하는 모델로 표현하면 전류가 CL을 통해 흐르고 특정 지연시간 JITTER를 유발한다.

만약 In이 white spectrum을 가진다면 Δt 또한 화이트 노이즈 성분을 갖는다

결국 white current noise가 white phase noise로 변한다.

*white : 주파수에 의존하지 않는 노이즈

인버터 N개가 직렬로 연결되는 경우 지터와 위상 노이즈는?

인버터들은 독립적인 uncorrelated 잡음원을 가지고 있어

전체 phase nois는 N 배증가,

rms jitter는 sqrt(N) 배 증가하게 된다.

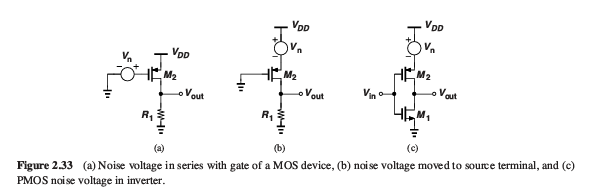

(예제 2.18) cmos inverter에서 M2 의 flicker noise를 고려해보자. 노이즈는 gate-referred voltage 로 모델린했다. 인버터가 동작에 어떤 변조를 일으키는지 보자

a) pmos이고, 게이트에 Vn이라는 flicker 노이즈가 직렬로 인가된다고 가정했다.

M2는 Vn을 증폭시키는 Common source 증폭기로 동작한다. 게이트 노이즈 Vn 이 증폭되어 출력에 영향

b) 회로 해석편의를 위해, channel length modulation이 무시가능할 경우 이 노이즈 전압Vn을 소스단자에 이동시킬 수 있다. 이는 Common gate 로도 해석 가능하며 Vn이 동일하게 증폭되어 출력에 영향을 준다.

결국 a b 는 equivalent 하다

c) 인버터 구조에 적용하여 Vn이 전원 VDD 에 직렬로 연결되어 있다고 해석할 수 있다.

noise가 전원에 나타나, delay를 발생시킨다.

결과적으로 phase noise가 노이즈 전압 Vn의 스펙트럼을 그대로 따른다.

flicker 노이즈는 1/f 형태이므로 위상노이즈도 10dB/dec으로 감소하는 특성을 갖는다.

delay line의 구조를 링 오실레이터로 만들때 위상노이즈의 변화

한 Inverter의 pmos에 노이즈 전압 Vn이 연결되어 있다고 하자.

두번째 inverter에 Vn 때문에 delay 가 생긴다. 이는 링 오실레이션의 oscillation 주파수 f0이 바뀐다는것을 의미한다.

f0 는 delay의 합에 반비례 하기 때문이다.

=> Vn은 delay 를 주어 frequency noise를 바꾼다.

주파수 노이즈가 위상 노이즈로 변화하려면 spectrum은 *(2πf)^2로 나뉜다

그래서 링 오실레이터의 phase noise 는 1/f^3에 비례하고 이는 -30dB로

플리커 노이즈에 의한 phase noise는 delay line에서의 flicker 노이즈로 인한 스펙트럼 감소보다 더 가파르게 감소한다.

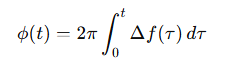

* (2πf)^2로 나뉘는 이유

위상은 주파수의 적분이다.

ω0=2πf0: 이상적인 중심 주파수

: 시간에 따라 변화하는 위상 잡음 (phase noise) 일때

위상은 주파수 적분

이때 신호의 스펙트럼을 보기위해 PSD(power spectral density) 를 보면

주파수 잡음 Δf(t)의 PSD를 SΔf(f)

위상 잡음의 ϕ(t)의 PSD를 라고 할 때,

적분은 주파수 영역에서 (라플라스) 1/s = 1/jw = 1/j2πf 가 된다.

주파수가 클수록 위상에 미치는 영향은 작다. 주파수 노이즈는 위상에 누적되나, 고주파 영역에선 영향을 덜 줌

2.4.3 LC Oscillators

CH1에서 배운 cross coupled LC oscillator에는 여러 위상 노이즈원인이 존재한다.

여기서는 thermal noise를 다룬다.

다음 회로는 트랜지스터 M1의 잡음전류 In1을 모델링한 것이다. 이는 M1의 열잡음 전류를 모델린 한것이다.

노이즈 전류 In1은 노드 X에 주입되어 지터를 유발한다.

X노드의 전압이 변하면 tank 회로 L1 L2 C 의 위상도 바뀌어 Phase noise가 발생한다.

M1이 꺼져있으면 In1은 0 : M1꺼져있으면 전류가 흐르지 않아 잡음도 없다

M2가 꺼져있으면 In1이 탱크회로로 흐르지 않는다. : M2 꺼져 In1이 Iss로 빠진다. -> 출력위상 영향없음

따라서 In1이 항상 출력위상에 영향을 주는 것은 아니다

시간에 따라 강도가 달라지는 노이즈 소스이다. - 어느타이밍에 노이즈가 발생하는지가 중요함

추가 노이즈 원인 : flicker noise, Iss노이즈

M1, M2의 플리커 노이즈도 출력위상에 영향줄 수 있다. 저주파 잡음

바이어스 전류원 Iss의 열/플리커 노이즈도 변환 경로에 따라 위상 노이즈로 바뀔 수 있다.

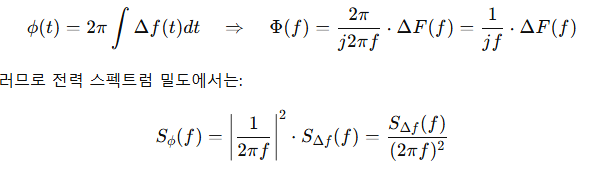

2.5 Effect of Jitter on Performance

Jitter는 앞에서 봤듯이 시간 도메인에서 클럭 엣지 위치가 ideal한 crossing point를 벗어나는 것이다.

보통 클럭, 데이터 전송, 샘플링 과 관련된 회로에서 성능을 저하시킨다.

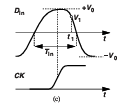

a) 이상적인 경우 Din이라는 랜덤 이진 데이터가 있고, CK클럭이 FF에 샘플링

CK의 상승엣지에서 Din을 읽어 Dout으로 전달 , 지터없음

b) 클럭지터 발생

상승엣지가 시간적으로 앞당겨지거나 늦춰짐

클럭이 너무 빨리샘플링 : 바뀌기 전 Din을 읽어 샘플링 오류 Dout 에러

데이터 유효시간은 Unit interval = Tin 으로 클럭지터가 UI 의 절반이상이면 오류발생위험 존재

c) 실제 파형

Din도 완벽하지 않고, transition 시간이 걸림

클럭이 데이터 전송 중간 t1에서 샘플링하면, 읽은값이 중간전압 V1으로 불완전하게 인식됨

FF이 metastability 에 빠질 수 있다.

Dout이 제대로 1,0 으로 구분되지 않는 문제 발생

더 복잡한 상황

1. 데이터 자체에 지터 있는 경우

: Din 타이밍과 CK타이밍이 asyncronise 할 경우 - 더 높은 에러가능성

2. skew

:CK와 Din 경로의 지연차 -> CK엣지가 좌우로 이동

스큐는 설계상 불균형에서 발생

유효지터마진 줄임

2.6 Effect of Phase Noise on Performance

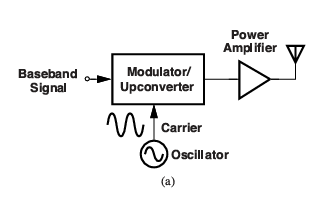

1. 송신기(TX)에서 위상 노이즈의 영향

동작 설명 :

베이스밴드 신호는 변조기(Modulator)와 업컨버터(Upconverter)를 통해 반송파(Carrier)에 실림

Carrier 는 오실레이터에서 생성되고, 증폭기(PA)를 거쳐 안테나로 전송

b) 이상적인 경우의 출력스펙트럼

phase noise가 없는 oscillator라면, 신호가 channel bandwidth(채널 대역폭) 내에서만 존재

예: Bluetooth의 경우 1 MHz 대역폭

c) 위상 노이즈가 있는 경우

phase noise 가 있는 oscillator인 경우, 오실레이터에 위상노이즈 φₙ(t) 가 추가되어 신호가 양옆으로 퍼짐( skirts )

다른 사용자 신호 f1을 간섭하게 됨 (blocker)

이로인한 문제점 : 다른 사용자의 약한 신호가 강한 TX신호의 phase noise에 묻혀 수신 불가

설계시 고려 : TX의 Phase noise가 다른 채널에 영향 끼치지 않게 작아야함

2. 수신기(RX)에서 위상 노이즈의 영향 (Fig. 2.38)

(a)RF reciever RX (수신기)

- 원하는 신호 f1과 강한 blocker f2가 같이 존재하는 상황

- rx가 약한 f1 주파수 신호에 관심있다면, 신호들과 오실레이터의 출력 f1을 time domain에서 곱함(mixing)

- 주파수영역에서 mixing은 원하는 채널의 중심을 0Hz로 바꾸고, 간섭신호는 ±(f₁ − f₂) 에 나타나게

( 이러한 동작을 우리는 믹서가 RF 입력을 '다운컨버전(downconvert)' 한다고 표현한다.' )

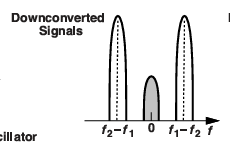

b) 이상적인 오실레이터의 경우

다운컨버전 후 f₁은 0Hz에, f₂는 ±(f₂ - f₁)에 나타남

두 신호가 깔끔하게 분리되어 있음

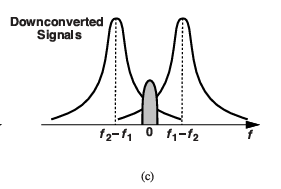

c) phase 노이즈가 있는 오실레이터라면

오실레이터의 위상 노이즈로 인해 블로커의 노이즈 스커트가 확장

결과적으로 블로커 신호의 노이즈가 원하는 채널까지 침범 (reciprocal mixing)

이로 인해 약한 신호가 오염됨

reciprocal mixing: 수신 오실레이터의 위상 노이즈가 인접 채널 간섭을 유발

휴대폰 수신기 등에서는 아주 낮은 phase noise 요구됨

3. 위상 노이즈가 신호 자체에 끼치는 영향

- 위상 노이즈 φₙ(t)는 원래 신호의 위상 θ(t)를 직접 오염시킴

- 예를 들어, θ(t)가 90° 단위로 바뀌는 QPSK의 경우 : 위상 노이즈가 누적되어 90° 이상 되면 신호 해석 불가

- 복잡한 변조(QAM, OFDM 등)는 더 엄격한 phase noise 제한 (예: rms < 1°)

학습 후 체크 포인트

- Ring vs LC 잡음 구조 차이