이것저것

Design of CMOS PLL Ch3(4) 본문

3.4 Phase Noise Considerations

설계에서 발진주파수, 전력소비, 전원민감도뿐만아니라 이제는 Phase noise 까지 고려하여 설계해보자

<위상 잡음 분석의 시작점>

- 기준으로는 22.6GHz 발진기 사용 (지난 포스팅에서의 reference design)

- 이후 위상 잡음 성능을 다음 4가지 방식으로 2GHz로 낮춘 구조들과 비교

<공통 시뮬레이션 조건>

- 공정 코너 : SS (Slow-Slow)

- 온도 : 75°C

- 공급 전압: 0.95V

- worst case 조건으로 위상잡음 비교 진행

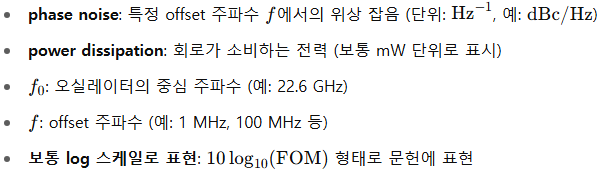

<핵심 개념 리마인드>

- phase noise 는 전력과 트레이트 오프 관계를 가진다 : 더 많은 전력을 소비할수록 위상잡음이 낮아진다

- 위상잡음은 발진주파수와도 관계있다.

일반적으로, 높은 주파수에서는 위상 잡음도 커지며

특히 저주파수에서는 flicker noise (1/f 노이즈) 영향이 커짐

<연결 공식>

(Chapter 2 및 식 3.14~3.15 참고)

예제 비교가 의미하는 것

- 동일 조건에서 전력과 위상 잡음 간의 trade off 를 구체적으로 보여준다.

- 4가지 방식 각각에 대해 phase noise 비교, 전력효율과 상호작용 분석, 어떤방식이 더 실용적인지 판단기반 제공

예제 3.7) 발진기의 phase noise 를 3dB감소시키는 방법은?

(3dB감소는 파워스펙트럼 상에서 잡음세기를 1/2로 줄이는 것이다.)

방법1) 두 oscillator의 출력을 합산

1) 기본 아이디어

- 주파수 f0으로 동작하는 서로 동일한 두 발진기 출력합침

- 각각 위상잡음이 ϕn1,ϕn2라고 하면, 이 둘은 서로 무관한 잡음원에서 기인하므로 uncorrelated

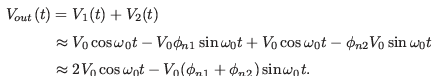

2) 수식유도

두 출력 : V1(t)=V0cos(ωt+ϕn1) / V2(t)=V0cos(ωt+ϕn2)

합산 후 출력 :

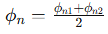

3) phase noise의 파워 스펙트럼

즉 3dB감소

4) 단점 : 이 방식은 실제로는 mismatch 문제로 구현 어렵다. 두 oscillator의 위상과 주파수가 완벽히 맞아야하고 그렇지않으면 성능이 오히려 악화된다.

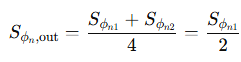

방법 2) Linear Scailing (선형 스케일링)

1) 핵심 아이디어

- 회로의 전체 전류, 소자 폭, 커패시턴스 등을 일정 비율로 스케일링함

- 예: 모든 W, I, C를 2배 증가시키고, 인덕턴스와 저항은 1/2배로 줄임

2) 결과

- 전압 스윙은 유지됨 (전류 × 임피던스 = 일정)

- 발진 주파수도 동일함 (LC, RC 상수 유지)

- 노이즈 전류는 2배 증가하지만,

임피던스 제곱과 곱하면 위상 잡음은 절반으로 감소

-> 마찬가지로 3dB위상감소

위상 잡음을 3dB 줄이려면, 전력 소비를 2배로 늘리는 방식이 일반적이다.

이는 전력-위상잡음 간 트레이드오프를 보여주는 고전적인 설계 전략이다.

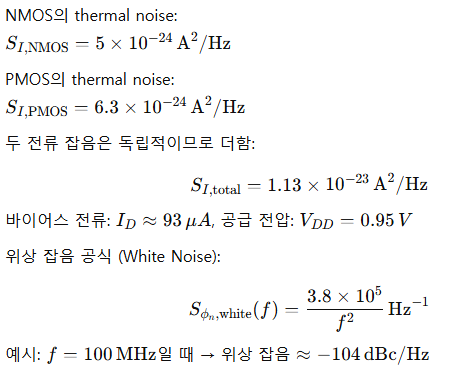

3.4.1 Transistor Noise Simulations

transistor수준에서 phase noise의 근원이 되는 power spectral densities of the drain current 시뮬레이션을 통해 구체적으로 분석해보자

위상 잡음 Sϕn(f)은 식 (3.14) 및 (3.15)에서 보듯이

→ 트랜지스터 드레인 전류 잡음 스펙트럼 SI(f),S1/f(f)에 비례함

그래서 phase noise 를 예측하기 위해서는 먼저 노이즈 전류 스펙트럼을 알아야한다.

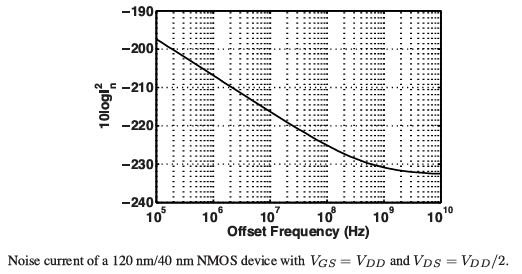

< NMOS (120nm / 40nm) 트랜지스터 분석 >

1) 시뮬레이션 조건 : VGS=VDD / VDS=VDD/2

2) 시뮬레이션 결과 : gm=0.22mS , ID=92 μA , WLeffCox≈120nm×36nm×17fF/μm^2

-> 게이트 면적 약 4.37 ×10^−15F

3) 1 MHz에서의 노이즈 전류

: S(f=1 MHz)=−207 dB=2×10−21 A^2/Hz

4) Flicker Noise 계수 계산

5) Thermal noise floor 확인

Flicker noise가 -10 dB/dec으로 감소하다가 이와 교차하는 지점 : 약 500MHz

-> 이 주파수가 flicker noise corner frequency

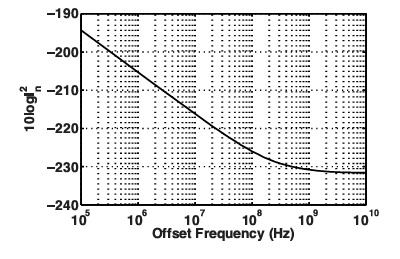

< PMOS (240nm / 40nm) 트랜지스터 분석 >

1) 조건 : ∣VGS∣=VDD, ∣VDS∣=VDD/2

2) 시뮬레이션 결과 ID=95 μA, gm=0.29 mS -> PMOS가 NMOS보다 gm이 약간 더 큼

Flicker noise corner : 약 650 MHz

→ PMOS가 flicker noise가 더 크다는 점이 핵심.

→ 특히 게이트 면적으로 정규화(normalized) 했을 때 더 명확히 보임

(요약)

위상 잡음 예측을 위해 트랜지스터 단위의 노이즈 특성이 필요함

NMOS, PMOS 모두에서 thermal noise는 −234 dB 수준

Flicker noise는 PMOS가 더 큼 → 회로 설계 시 PMOS의 영향을 고려해야 함

Corner frequency는 NMOS가 낮고, PMOS가 약간 높음 (500MHz vs 650MHz)

(설계시)

PMOS의 flicker noise가 상대적으로 더 크므로, NMOS만으로 구성된 회로가 위상 잡음에 더 유리

혹은 면적을 키워 flicker noise를 낮추는 방법도 고려

예제 3.8) 트랜지스터의 드레인 전류 잡음에서 flicker noise corner frequency가 500 MHz일 때,

링 오실레이터 전체의 위상 잡음 corner frequency도 같을까?

배경) flicker noise corner frequency란?

low frequency에서 1/f 잡음이 thermal noise보다 우세한 구간

= 플리커 노이즈 영역 (1/f³) 과 열잡음 영역 (1/f²)이 교차하는 지점

- flicker noise 구간: 기울기 ≈ –30 dB/decade (1/f³)

- white noise 구간: 기울기 ≈ –20 dB/decade (1/f²)

이 지점을 기준으로 위상 잡음이 1/f^3에서 1/f^2로 바뀜

답변) 같지않다 phase noise corner frequency 가 더 낮아진다

이유:

- 위상 잡음 스펙트럼은 식 (3.14), (3.15)를 기반으로 함

- 링 오실레이터는 여러 개의 인버터로 구성되어 있고,

각 인버터의 잡음이 종합되어 평균화됨 - 즉, 위상 잡음의 corner frequency는 트랜지스터보다 더 낮음

오프셋 주파수

: f = 오실레이터의 캐리어 주파수 f0 으로부터 얼마나 떨어진 주파수 위치에서 phase noise 를 측정하는지를 의미

ex) 오실레이터가 22.6 GHz에서 동작한다면,

1 MHz offset은:

→ 22.601 GHz 또는 22.599 GHz 지점에서의 위상잡음을 의미합니다.

100 MHz offset은:

→ 22.700 GHz 또는 22.500 GHz에서의 위상잡음을 말합니다.

Phase noise는 carrier 주변에서 가장 심하고, offset 주파수 멀어질수록 줄어든다.

보통 표준 offset 1MHz,100MHz 등의 표준 offset에서 phase noise값 비교한다.

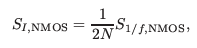

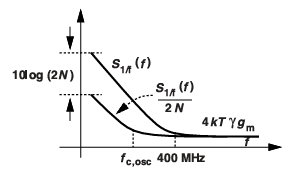

수식유도 요약)

1. Thermal noise 항 : (식3.14)

2. Flicker noise 항 : (식 3.15)

3. 두 항이 같아지는 코너 주파수 를 구함 (코너주파수 : 두 종류의 잡음이 교차하는 지점의 주파수)

→ 트랜지스터와 비교했을 때, corner frequency가 1/2N배로 낮아짐

4. 수치 적용 (3단 링 기준)

2N = 6

트랜지스터 corner : 4kT γgm = [g2 mK/(WLCoxfc,osc)]/(2N) -> fc = 500MHz

5. 그림 해석

S1/f : 단일 트랜지스터의 잡음 스펙트럼

S1/f /2N : 링 오실레이터의 잡음 스펙트럼

-> thermal noise수준은 동일하나, flicker 노이즈 항이 2N배 작아짐

-> 결과적으로 corner frequency가 왼쪽으로 이동

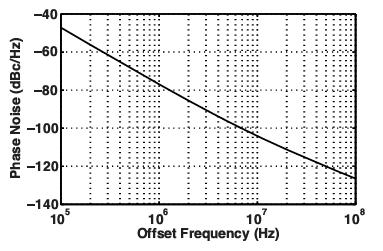

3.4.2 Reference Oscillator Phase Noise

앞에서 설계한 22.6GHz의 reference oscillator의 phase noise를 알아보자.

- offset이 100kHz → 1MHz → 10MHz로 증가할 때, 각 decade마다 위상 잡음이 약 30dB씩 감소 중

- 이는 flicker noise가 upconversion 되어 1/f^3 slope를 따름을 의미

- flicker noise 구간: 기울기 ≈ –30 dB/decade (1/f³)

- white noise 구간: 기울기 ≈ –20 dB/decade (1/f²) - 90 MHz 부근에서 기울기가 –20 dB/dec으로 바뀝니다 => 이 지점을 corner frequency ≈ 90 MHz 로 추정

- 시뮬레이션으로 얻은 코너주파수 90MHz는 PMOS의 잡음 기여로 인해 이론값(67MHz)보다 높음

(이론으로는 nmos만 계산했음)

- 위상 잡음은 1MHz offset에서 −47 dBc/Hz, 매우 높은 편

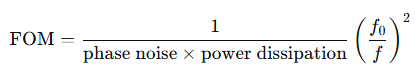

- phase noise 클수록 성능이 나쁜데 단순히 크다고 비교할 수는 없고 전력소모와 주파수에 따라 FOM으로 비교해야한다,

<FOM, Figure of Merit>

- 다른오실레이터끼리, 그리고 다른 공정에서도 객관적 성능 비교를 위해 FOM (Figure of Merit)를 정의

- 공식 : 주파수, 위상 잡음, 소비 전력을 함께 고려하여 비교 가능

- 주의점 : 1/f 잡음구간보다 white noise 구간(높은 offset 주파수) 에서 더 좋은값이 나오는 경향

위상 잡음이 f^3 -> f^2 로 감소하며, 시스템이 더 안정화 되기때문

Phase noise 는 앞선 공식 활용

- 이론적 위상 잡음 계산 결과:

1) spectrum of thermal noise:

*f0 = 22.6GHz

2) flicker noise:

- white noise는 high-frequency에서,

flicker noise는 low-frequency에서 지배적입니다. - flicker noise의 기울기: 1/f^3, white noise의 기울기: 1/f^2

ex 3.10) f = 1 MHz and f = 100 MHz 에서의 FOM을 계산하라.

* 보통 offset frequency를 f = 1 MHz and f = 100 MHz 에서의 phase noise 를 많이 비교함

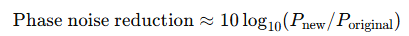

ex3.11) 100MHz의 오프셋 줖수에서 -120dBc/Hz phase noise 를 얻기위해서 같은 oscillaiton frequency 라고 하면 어떤것을 오실레이터에서 수정해야할까?

sol) 현재 phase noise : -104 dBc/Hz at 100 MHz offset => 목표 : -120 dBc/Hz

16dB만큼 phase 가 줄어들어야한다.

=> 결국 Phase noise 를 줄이기 위한 방법을 고민해야함

1. Power Phase noise trade off

phase 노이즈는 power를 키우면 줄어든다.

16dB의 노이즈를 줄이기 위해 Pnew/Poriginal=10 ^1.6 ≈ 40

전력의 비가 10 ^1.6 되게 하면 된다. 그래서 전력을 40배 키워야한다.

2. transistor 사이즈 조정

40배로 전력을 키우기 위해, 모든 트랜지스터의 width를 40배 키워준다.

그러면 gm도 커지고 , Id도 커지고 그래서 파워도 커진다, 그리고 크기 커서 기생성분도 커진다.

3. 전력 소모 power consumption (Id x VDD)

원래 power : P= 60 μA×0.95 V= 57 μW

수정후 power : P=40×57 μW=2.3 mW

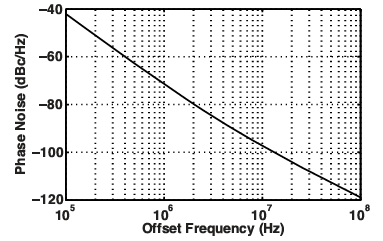

=> phase noise 곡선은 16dB shift 된다.

=> 오실레이터 주파수는 그대로이다.

=> 회로 사이즈와 파워는 크게 증가한다.

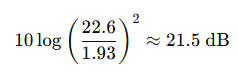

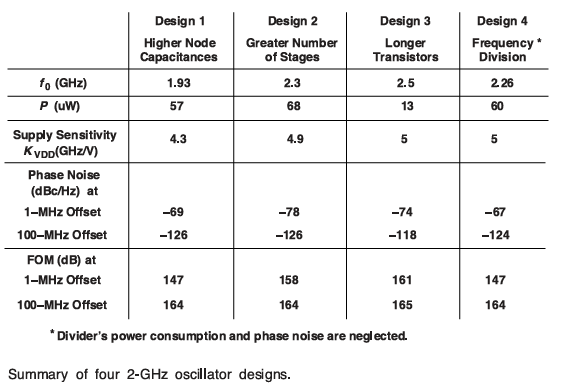

3.4.3 첫 번째(Add capacitance) 2-GHz 설계 Phase noise

앞서 설계한 reference 회로의 내부 노드에 커패시턴스를 추가해 주파수를 낮춤 (1.93GHz)

전력소비는 그대로 두고 발진주파수 f0만 낮출 수 있다. 22.6 -> 1.93 GHz

phase noise :

위상 잡음 곡선(Fig. 3.22)은 기준 설계와 거의 21.5dB 차이

→ 이론적으로

만큼의 차이만큼 감소해야한다. 실제와 일치한다 .

결론 : phase noise 줄었지만, 주파수가 줄었기 때문 , FOM은 그대로 유지됨

3.4.4 두 번째(stage 수를 31개로 증가) 2-GHz 설계 위상 잡음

Fig. 3.15(a): 스테이지 수를 3 → 31로 증가, f₀ = 2.3GHz

위상 잡음이 Fig. 3.14(a)보다 약 9.2dB 더 낮음

- flicker 잡음 영역에서 훨씬 개선됨

이 방식은 잡음을 효과적으로 평균화함

결론: 같은 주파수를 유지하며 phase noise를 줄이려면 커패시턴스를 늘리는 것보다 스테이지 수를 늘리는 것이 더 유리

phase noise 가 줄고, 전력 소비는 크게 증가하지 않아서 FOM도 더 좋아짐

3.4.5 세 번째(nmos,pmos L길이 증가) 2-GHz 설계 위상 잡음

- Fig. 3.16(a): 트랜지스터 채널 길이를 증가시킨 설계 (L = 240nm)

- L을 늘리면 각 node capacitance가 작아지고 그결과 소모전력 작아짐

(why?) 오실레이터에서는 각 인버터의 출력이 다음 스테이지의 입력 게이트를 drive한다.

이때 출력 node 는 다음 gate의 input gate capacitance 때문에 부하를 받는다.

1. 입력 capacitance

Capacitance는 클수록 많은 전하를 충/방전 해야하므로 전력소모가 커지고 delay도 길어진다.

2. L을 늘리면 왜 Cgate 가 줄어들까?

단순히 위의 식만 보면 L이 늘어나면 Cgate도 커져야 하지만, 실제 회로에서는 아래 조건이 고려된다.

설계자는 일정한 drive 능력 또는 동작속도를 위해 W/L을 조정한다.

구동능력 :

L 이 커지면 => 구동력이 약해지므로 이를 보완하려면 W이 커져야한다.

이 회로에서는 의도적으로 drive 능력을 줄이기 위해 W를 그대로 두고, L만 키워서 설계를 진행함

이때 이론상 Cgate 값이 L늘어나니까 늘어나는게 맞는데 책에서 줄어든다고 한 이유는

W만 키우면 Cgate가 증가하고, L만 키우면 Cgate 증가하긴하지만 동시에 transister strength가 약해지고 회로의 전류와 파형특성이 바뀌어 node특성에 걸리는 effective capacitance는 오히려 줄어들 수 있다.

회로전체적으로 보면 L줄어서 Id 전류 줄고, 출력의 스윙 속도나 부하가 달라져, 결과적으로node cap이줄어들 수 있다.

소비 전력: 13µW (매우 낮음)

- f₀ = 2.5GHz, 위상 잡음은 기준보다 5dB 정도 더 좋음

KN, KP 값이 L에 따라 달라지므로 잡음도 감소함

분석 결과:

스테이지 수 증가와 채널 길이 증가 전략 모두 비슷한 수준의 FOM을 제공

그러나 채널 길이 증가 전략이 전력 대비 성능에서 더 우수

목표 위상 잡음(예: −100 dBc/Hz @ 1MHz)을 달성하려면:

트랜지스터 W를 대폭 키워야 하며, 이 경우 소비 전력은 8.2mW로 급증

면적과 전력 측면에서 비용이 큼

3.4.6 네 번째 2-GHz 설계 위상 잡음

- 분주기(counter) 사용해 출력 주파수를 나눔 -> 위상도 M으로 나뉨

- 위상 잡음도 M배 낮아짐 (20logM dB), 하지만 실제 jitter(초 단위)는 변하지 않음

- 따라서 FOM은 그대로 → 위상 잡음 감소는 상대적일 뿐

example 3.14: Jitter는 왜 안 줄어들까?

Jitter는 실제 시간 단위(초, ΔT)로 된 랜덤한 엣지(전압 변화)의 흔들림입니다.

-

- 오실레이터의 출력이 분주기(divider)를 지나도 이 시간상의 ΔT는 그대로 유지됩니다.

- 즉, divider의 출력에서도 여전히 ΔT초만큼 흔들림이 존재함.

그런데 왜 Phase Noise는 줄어들까?

- 위상(phase)은 시간 ΔT를 주기 T로 나눈 값에 비례합니다:ϕ=(ΔT/T)×2π

- phase 가 (ΔT/Tout)× (2π)이되는데, (ΔT/Tin)× (2π).보다 더 작은 값이 되는 것이다.

- 분주기로 인해 출력 주기 Tout 가 더 길어지기 때문에, 같은 ΔT라도 상대적으로 작은 위상 변화로 나타남.

→ 그래서 phase noise가 줄어든 것처럼 보이는 것

결론:

- FOM 개선이 목적이라면 channel length 증가가 가장 효과적

- 그 다음이 스테이지 수 증가

- 주파수 분주는 phase noise는 줄여주지만 FOM에는 별 도움 없음