이것저것

PLL system 관점/ 수식적 본문

PLL 시스템 전달함수

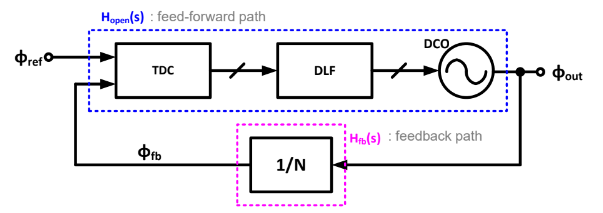

PLL 의 최소 블럭은 아래와 같이 표현 가능하다.

파란색 블럭을 우리가 기존에 아는 feedback 회로에서의 open loop 회로라고 가정하면

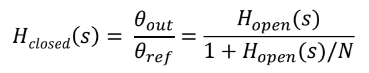

피드백 루프의 전달함수를 구하면 아래와 같이 구할 수 있다.

- DC gain은 N

- 전체 loop가 low pass filter의 특성을 가진채 동작함을 알 수 있다 .

간단표현

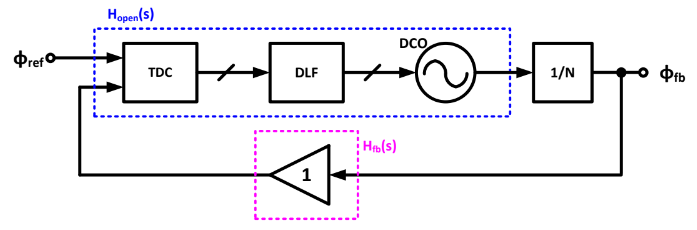

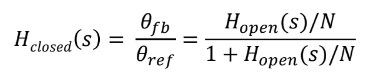

위 식은 feedback path 값이 복잡하므로, 간단하게 바꾸어 표현하면 아래와 같이 표현 가능하다.

- 대신 DC Gain이 1 로 바뀌게 됨

- Low pass filter 특성은 동일

TDC

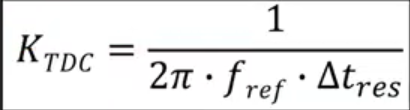

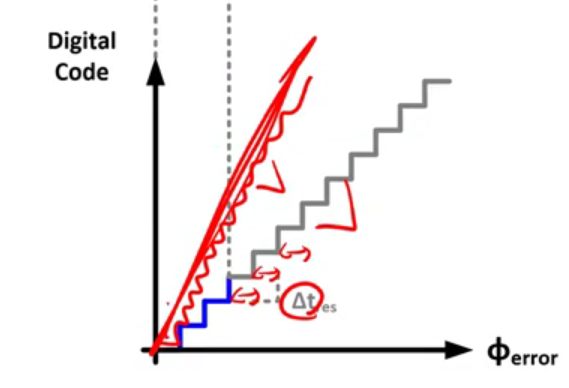

TDC의 gain K_TDC는 "위상 에러에 대해 디지털 코드가 얼마나 바뀌는가" 라고 정의 할 수 있다.

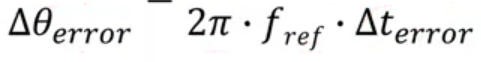

이를 수식적으로 표현하면,

- 위상의 변화 => Fref와 Ffb 신호 간의 시간차이를 2pift로 위상 차이로 변환시킴.

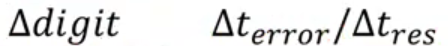

- 디지털 코드의 변화량 => 시간에러/ 시간해상도 => 해상도에 따라서 시간에러를 code 변환으로 나타냄

이를 정리해서 나타내면 오른쪽과 같은 최종 K_tdc 식을 구할 수 있다.

이 식의 의미를 정리해보면

f_ref : TDC에서 사용하는 ref 주파수 (pll 마다 결정되어 있음)

deta(t_res) : 시간 해상도

t_res에 따라 TDC gain 정해짐

-> 시간 해상도가 조밀할수록 TDC의 gain은 커진다

-> 해상도 작을 수록 위상 변화가 조금만 있어도 code 변화가 더 잘 변한다.

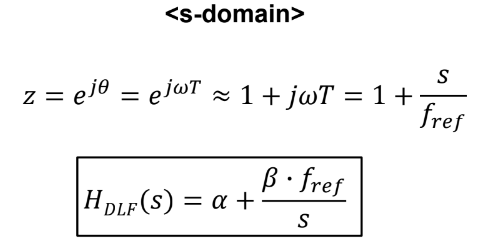

DLF

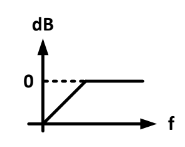

- 고주파 노이즈 제거해주는 역할

- clock 을 사용함 -> flip flop이용 -> z^-1 -> s파트 존재한다는 의미 -> 입력신호 변화의 빠르기에 따라(주파수) 시스템 반응크기나 위상이 달라짐 => 실제로 LF의 경우 빠르게 변하는 신호(고주파) 는 감쇄하고, 느린신호만 통과시킴

- : 한 클럭 지연

- : 지금 − 이전 → 차분 (미분)

- 1/(1−z−1) : 누적 → 적분

그래서 이렇게 s domain의 식으로 전달함수를 정리할 수 있다.

DCO

- 코드당 주파수를 얼마나 바꾸는가

- PLL 이므로 코드가 바뀌는 순간 주파수가 바뀜 -> 위상으로 보려면 적분해서 변화를 지켜봐야함 -> 적분 1/s

- rad 이므로 2pi 곱해주기

DCO 의 경우 Power 에 노이즈가 끼게 되면 자체 노이즈가 output 위상에 끼게 된다.

DCO의 신호에 노이즈가 꼈을때 전체 feedback 회로 까지 고려한 회로를 보게되면,

DCO로 Noise 입력 -> feedback으로 1/N -> Hopen(s) 오픈루프(TDC -> DLF -> DCO로 feedback 해서 - 해줌) -> 위상 출력

이때 Loop가 감당할 수 있는 속도보다 노이즈가 크면 노이즈가 그대로 위상에 반영됨,

loop가 감당할 수 있는 느린 속도라면 feedback성분으로 인해 노이즈가 감쇄됨. -> high pass fileter의 특징가짐

위의 식들을 가지고 system을 표현해보면 아래와 같다.

Hclosed(s) 식에 구한 전달함수들을 모두 대입하여서 구해보면 2차회로 식의 형태로 나타낼 수 있다.

이 특성 방정식을 이용해서 회로의 특성을 알아볼 수 있다.

=> PLL 을 설계한다는것 = Loop Filter의 계수 a.B 를 구하는 것과 같다.

- 실제 pll 설계시, 보통 system spec이 정해지면

- DCO의 spec(Kdco- 코드하나당 몇 주파수) 정해지게 됨,

- 출력 dco와 ref 얼마일지도 보통 정해져있음

- tdc 해상도도 pll inband 노이즈에 따라서 target 이 정해짐

- BW는 보통 ref clk의 1/20 or 1/10 이내로 정해져야함

- pll zeta(2차 시스템에서 damping factor) 값은 1을 넣으면 됨 (또는 0.707) -> 굳이 막 1이상으로 할 필요는 없음 신호가 갑자기 바뀌었을때 damping 하면서 좀 흔들려도 lock 만 되면 됨 (lock time은 손해볼 수 있음)

=> 이때의 a B 값을 구하는게 핵심이다.

a는 저항, B는 cap 이라고 생각하면 됨

보통 많이 크지는 않음

pll 설계 매커니즘

1. 어떤 구조로 설계할 것인가.

2. coefficient 정리

3. a B 구하기

--------------- -> 발산하지 않고 동작하는 pll을 만드는 것

4. pll 의 노이즈 특성 좋게 만들기

--------------- -> 노이즈를 줄이는게 더 나아가 pll 설계의 핵심